用过Allegro的读者一定知道,Allegro中有大量的颜色设定命令,大量的约束条件,而且在出Gerber文件时也需要做大量的设定。在不同的PCB设计中,这些操作是类似的,重复的,因此,如果能够建立PCB设计模板,将会大幅提升工作效率,并降低出错的概率。本文针对这一过程做简单阐述。

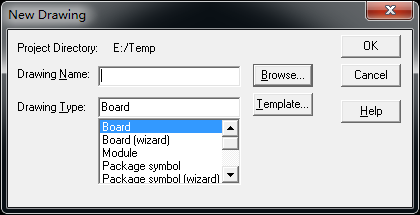

1. 创建一个空的PCB文件。运行Allegro,点击File—>New,在弹出的对话框中选择Board,如下图。

点击Browse,找到欲存放PCB文件的目录,本例中是E:/Temp目录下,并在弹出的对话框中输入文件名Template,如下图。

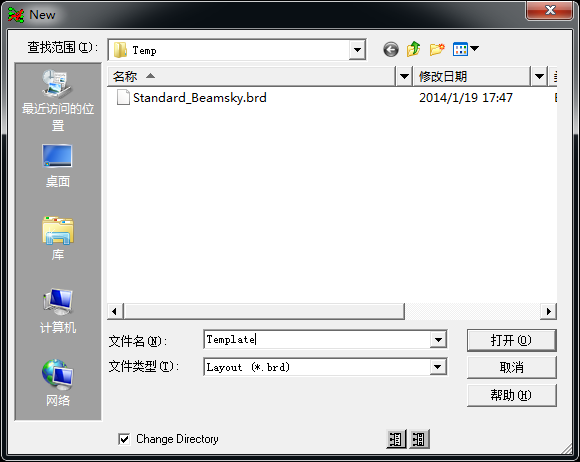

点击打开后,Allegro就创建完成了一个空的PCB文件,此时回到主界面,如下图。

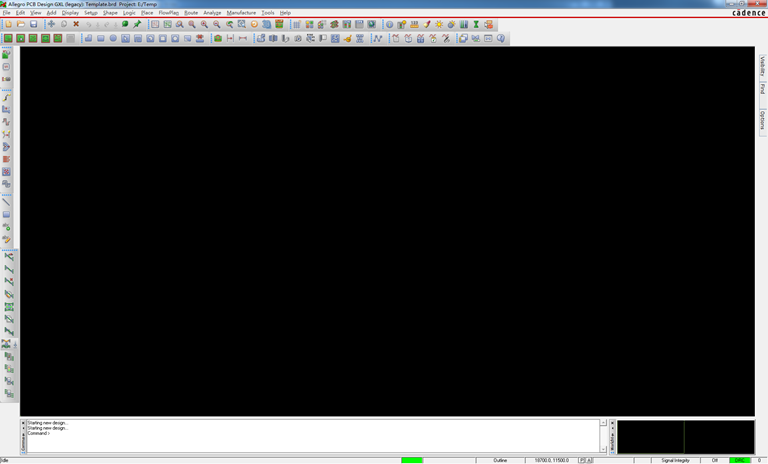

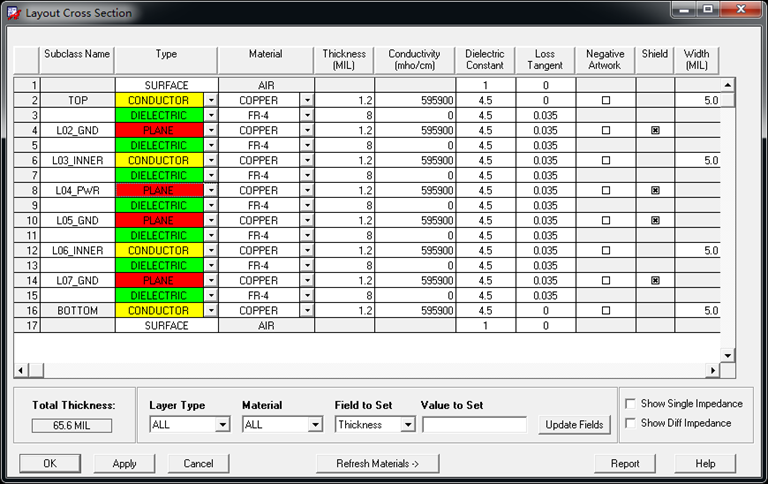

2. 变更PCB叠层。Allegro创建的PCB默认是2层板的,如下图。

2层板显然不符合一般的产品设计要求,在此将其变更为8层板,按照下图方式进行设置。

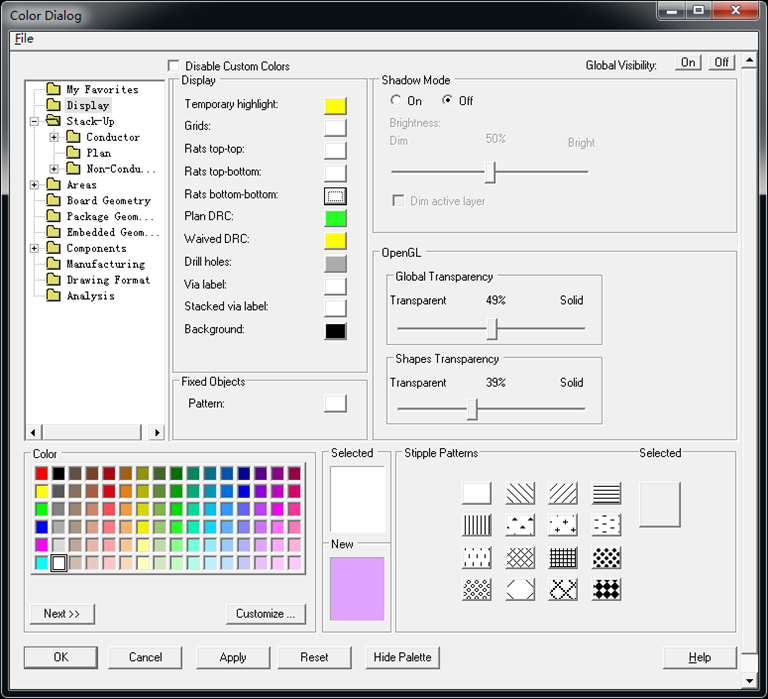

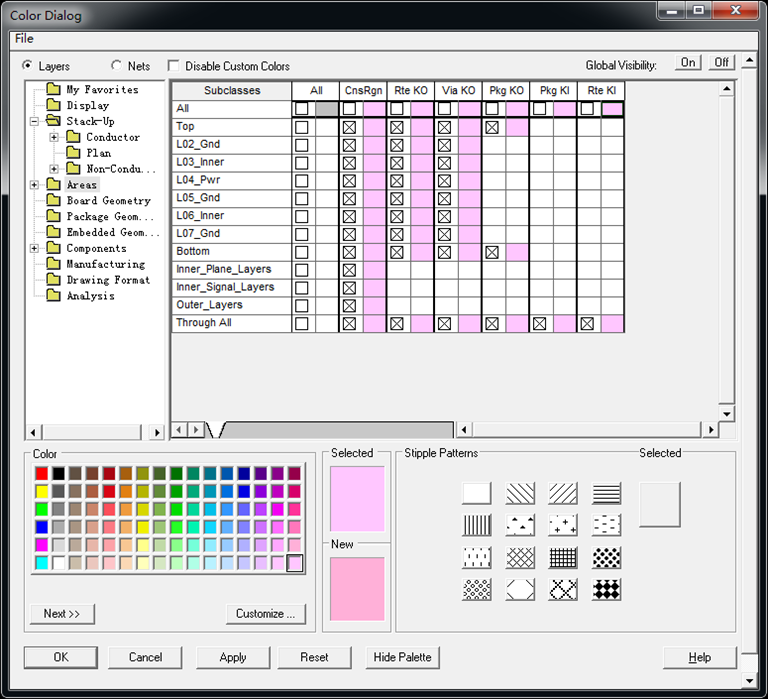

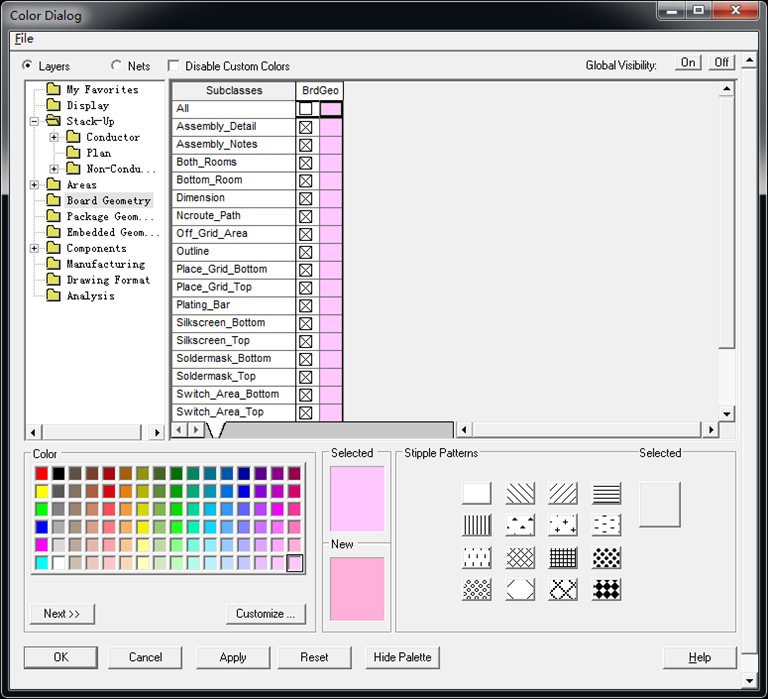

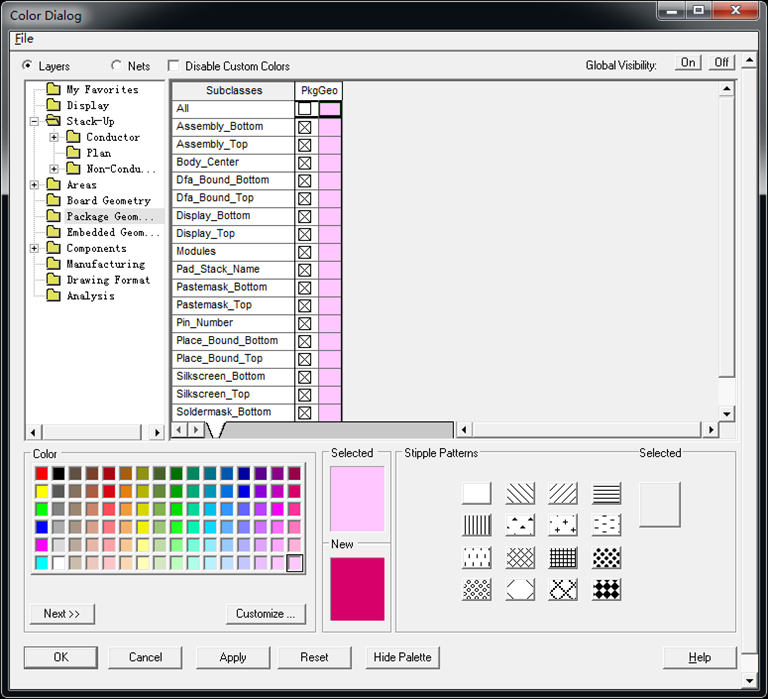

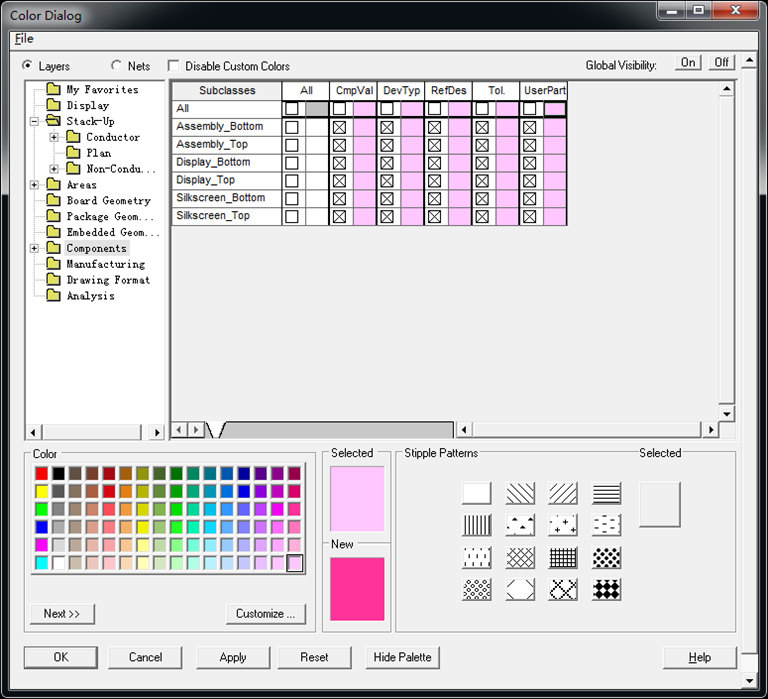

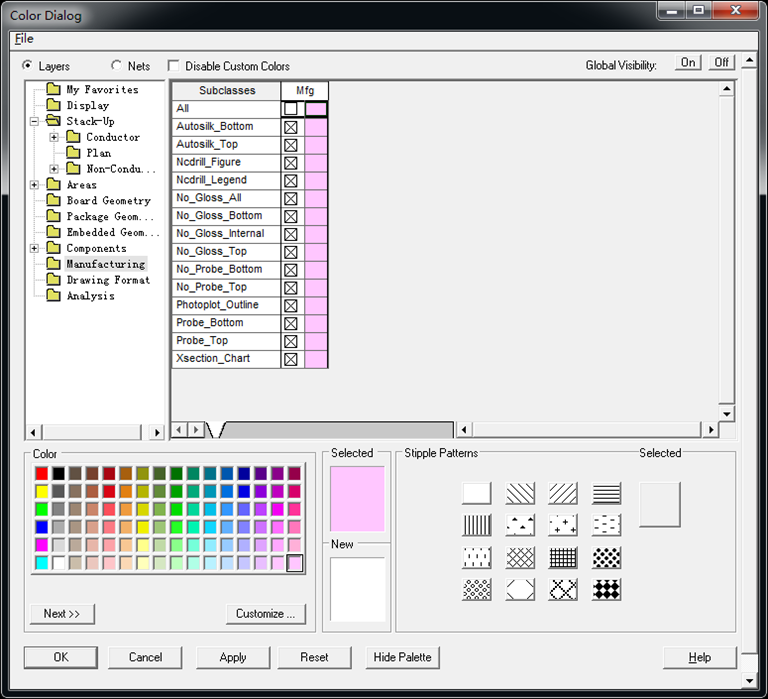

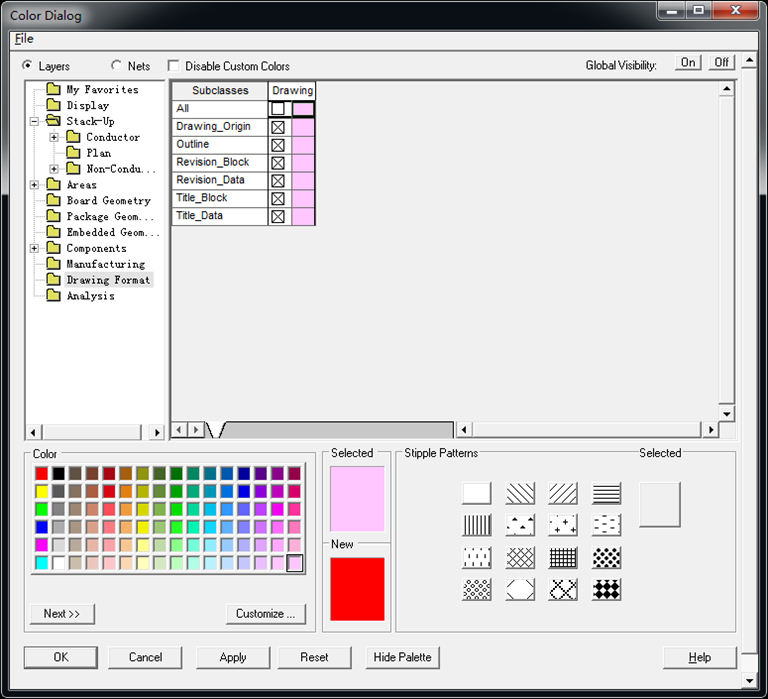

3. 变更颜色设定。Allegro中默认的颜色设定是大片的绿色,不知道各位读者是否习惯, 笔者本人是不太喜欢这样的设定。此处可根据个人习惯进行更改,以下图片是 笔者设置完成的颜色设定。

Display

Stack-Up

Areas

Board Geometry

Package Geometry

Components

Manufacturing

Drawing Format

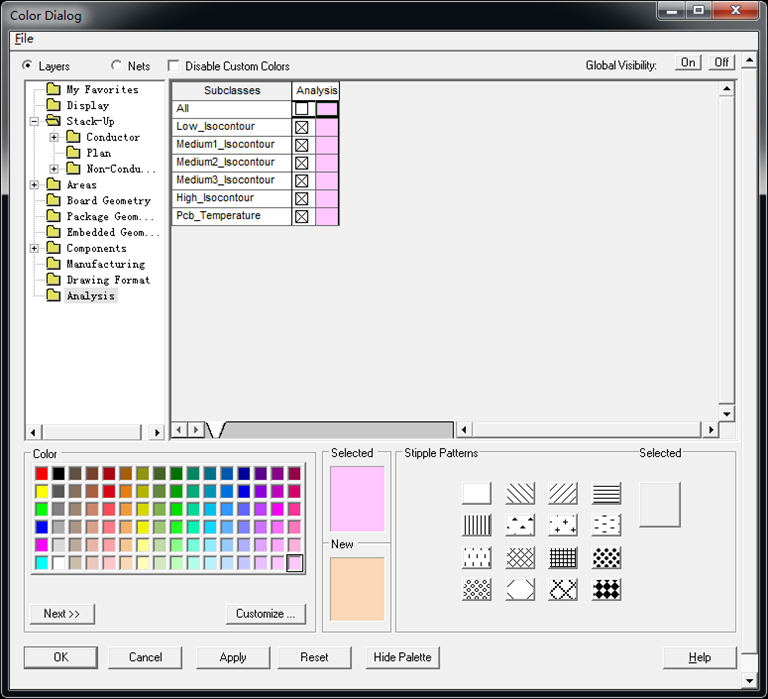

Analysis

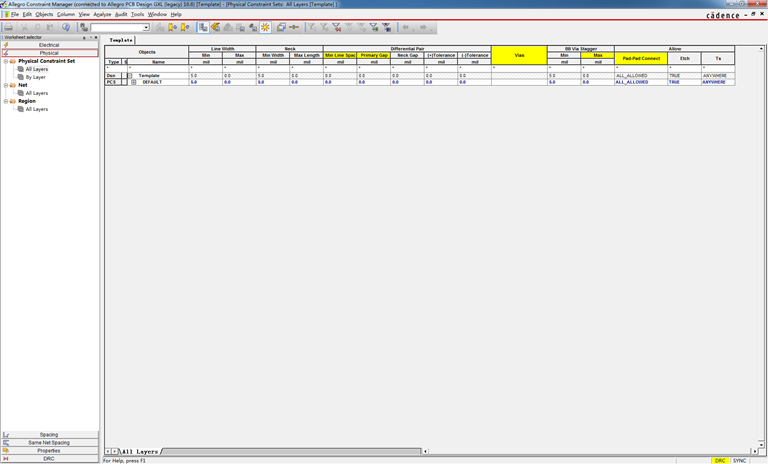

4. 变更约束条件。本文仅针对约束条件中的Physical属性变更做简要说明,Allegro默认的Physical属性如下图。

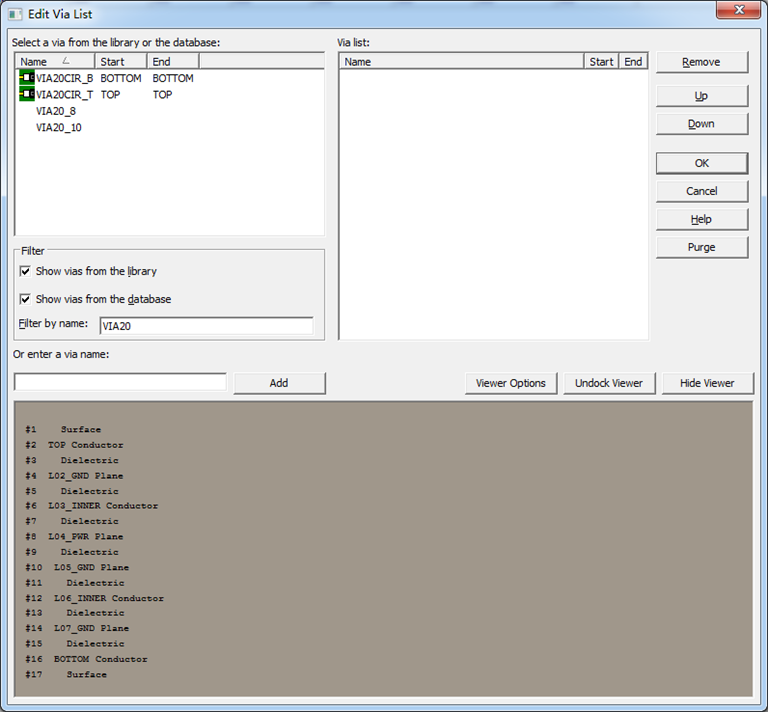

指定所使用的过孔。单击DEFAULT一行与Vias一列的交叉位置处,会弹出Edit Via List对话框,如下图。

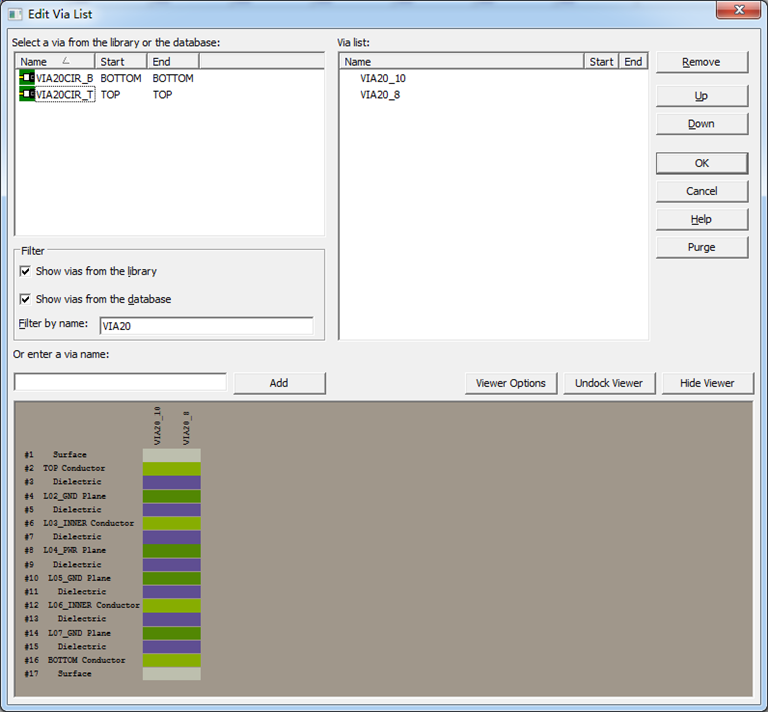

可以在Filter by name一栏中输入过孔名称进行过滤,如输入VIA20就会出现以VIA20*作为名称的全部过孔,包括VIA20CIR_B,VIA20CIR_T,VIA20_8,VIA20_10。注意这里出现的过孔是 笔者本机所指定的封装库中已经存在的过孔,如果读者没有相应的数据库或者未正确指定封装库所在路径,则无法出现这些过孔。双击需要使用的过孔,就可以将相应的过孔添加至右侧的Via list中,如下图。

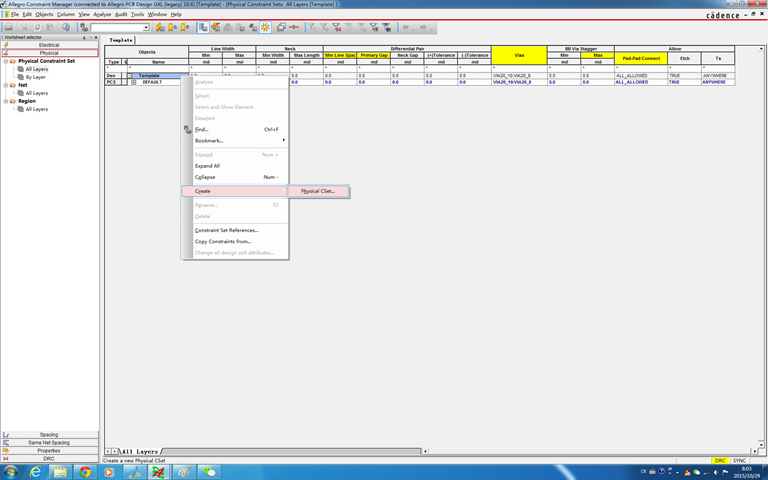

这些过孔的使用优先顺序还可以使用Up/Down命令进行调整。点击OK返回Constain Manager主界面,再为电源网络创建单独的Phsical属性。在Template上点击右键,然后依次点击Create—>Physical Cset,如下图。

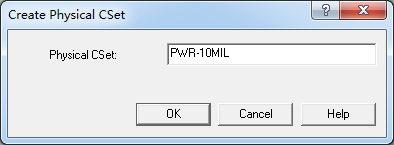

在弹出的对话框中将新的Cset命名为PWR-10MIL,如下图。

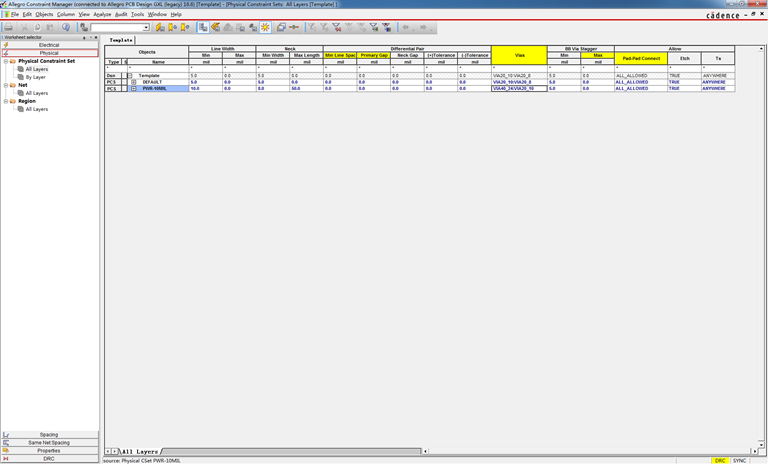

修改PWR-10MIL Cset对应的线宽为10mil,Neck为8mil,默认过孔为VIA40_24,可选过孔为VIA20_10,如下图。

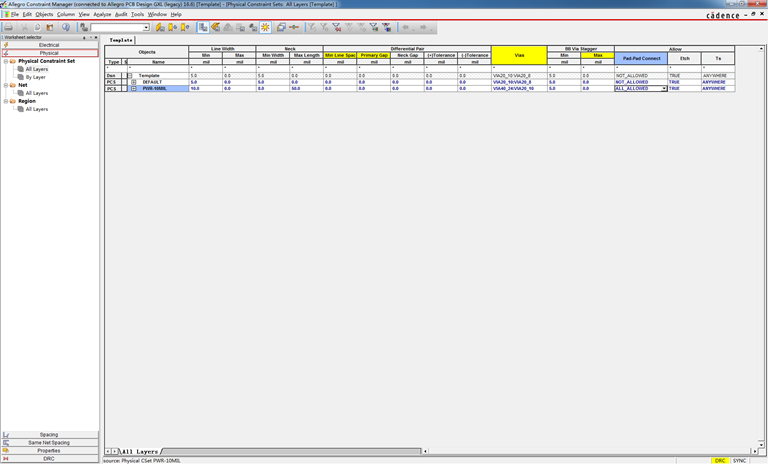

这里有一点需要指出的是,通常的PCB设计不允许过孔打在焊盘上,但对于芯片底部存在较大接地焊盘的情况,则不可避免,为了满足这样的条件,将DEFAULT对应的Pad-Pad Connect变更为Not Allowed,PWR-10MIL对应的Pad-Pad Connect变更为All Allowed,如下图。

Electrical的约束条件的设定只能是在网表导入之后进行,其他约束条件的设定读者可自行研究,可根据实际PCB设计规范,制板工艺等进行调整。

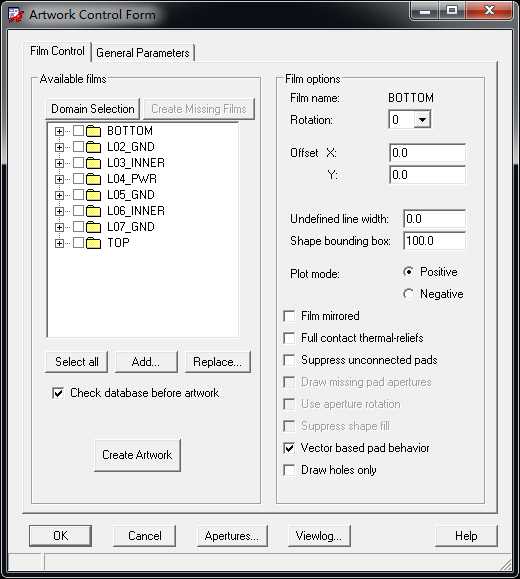

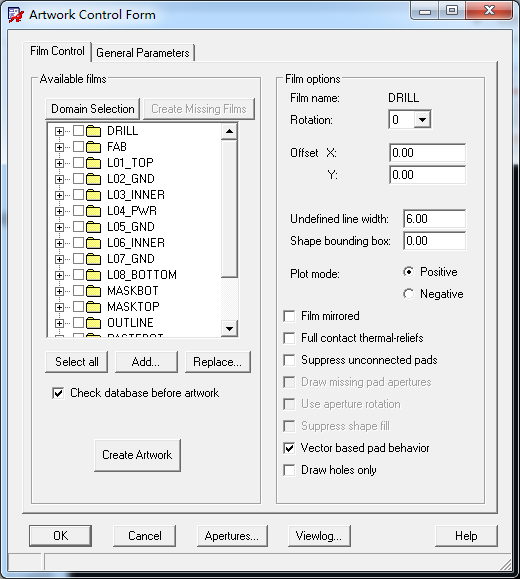

5. 设置Gerber文件。点击工具栏中的“照相机”图标,会弹出Artwork Control Form窗口,如下图。

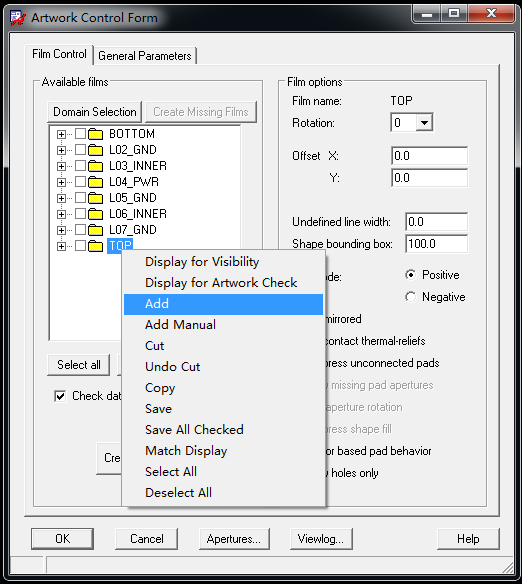

显然,如果只将这些Film输出是不够的。本文以顶层丝印为例,阐述增加输出Film的方法。在任意Film上面点击右键—>Add,如下图。

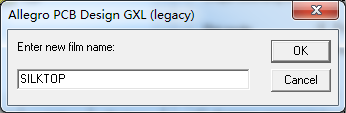

在弹出的对话框中输入新的Film名称SILKTOP,如下图。

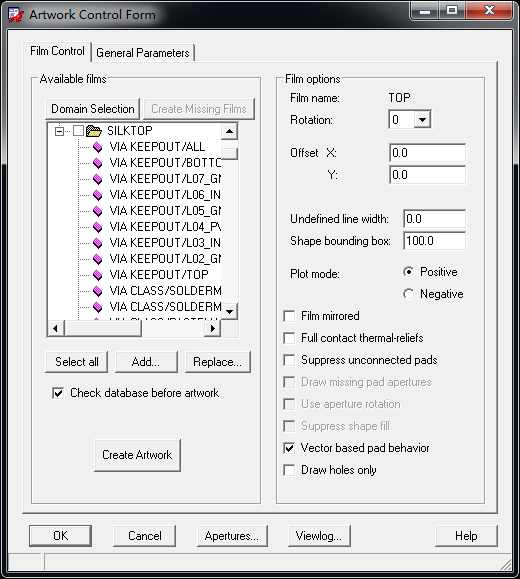

Artwork Control Form窗口,展开SILKTOP文件夹,发现其中出现了大量的层,如下图。

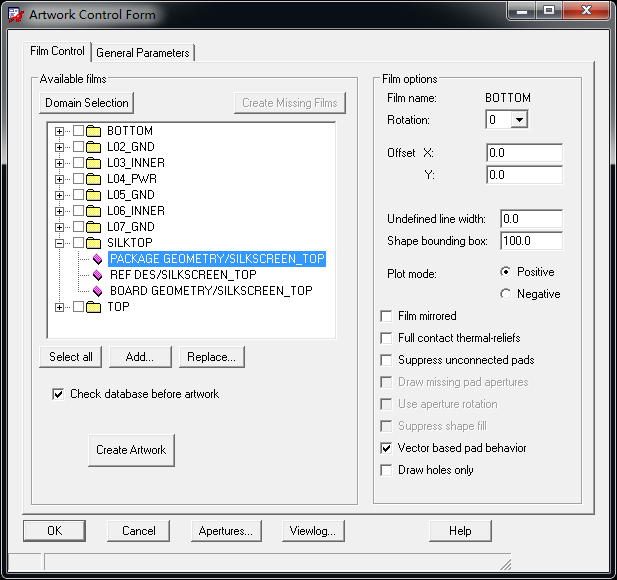

将其逐个删除,并添加PACKAGE GEOMETRY中的SILKSCREEN_TOP,REF DES中的SILKSCREEN_TOP,BOARD_GEOMETRY中的SILKSCREEN_TOP,完成后如下图。

按照类似方式,添加Soldermask,Pastemask,Outline等Film,完成后的设定如下图。

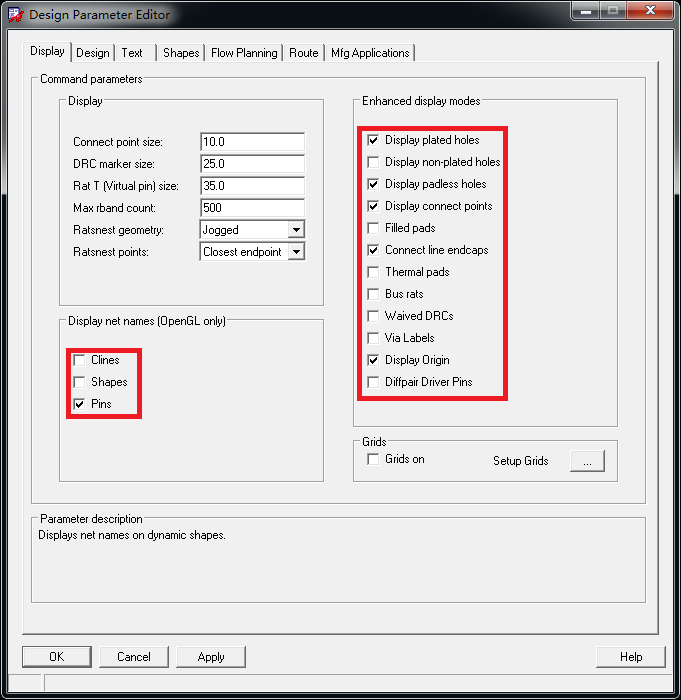

6. 其他设定。点击Setup—>Design Parameters,变更默认设置为个人习惯,如下图是 笔者常用的设置。

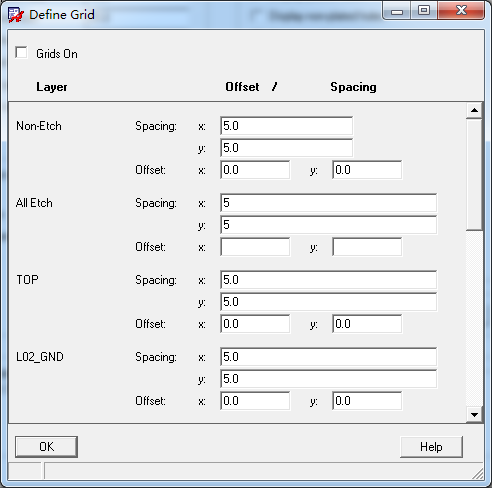

点击Setup Grids按钮,设置格点为5mil,如下图。

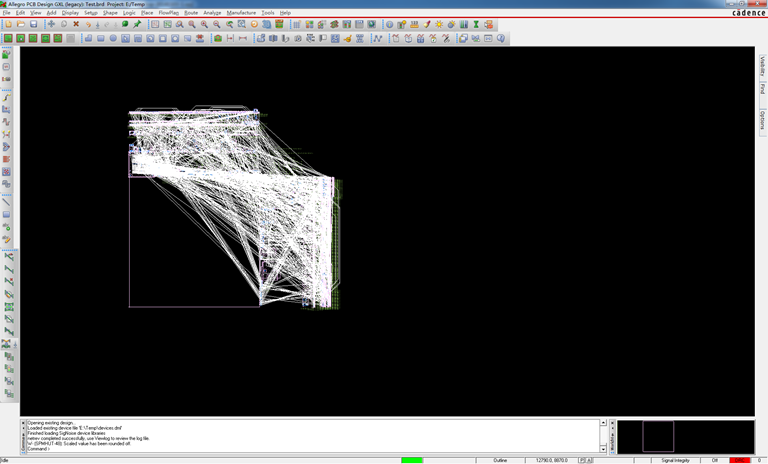

7. 到目前为止,已经完成了模板的建立。最后通过实际的PCB设计,对模板进行检验。将刚刚创建的Template.brd复制,命名为Test.brd。在Test.brd中随意设定Outline,并导入一份网表,完成后的效果如下图所示,读者可自行检查此前设定的规则是否正确。